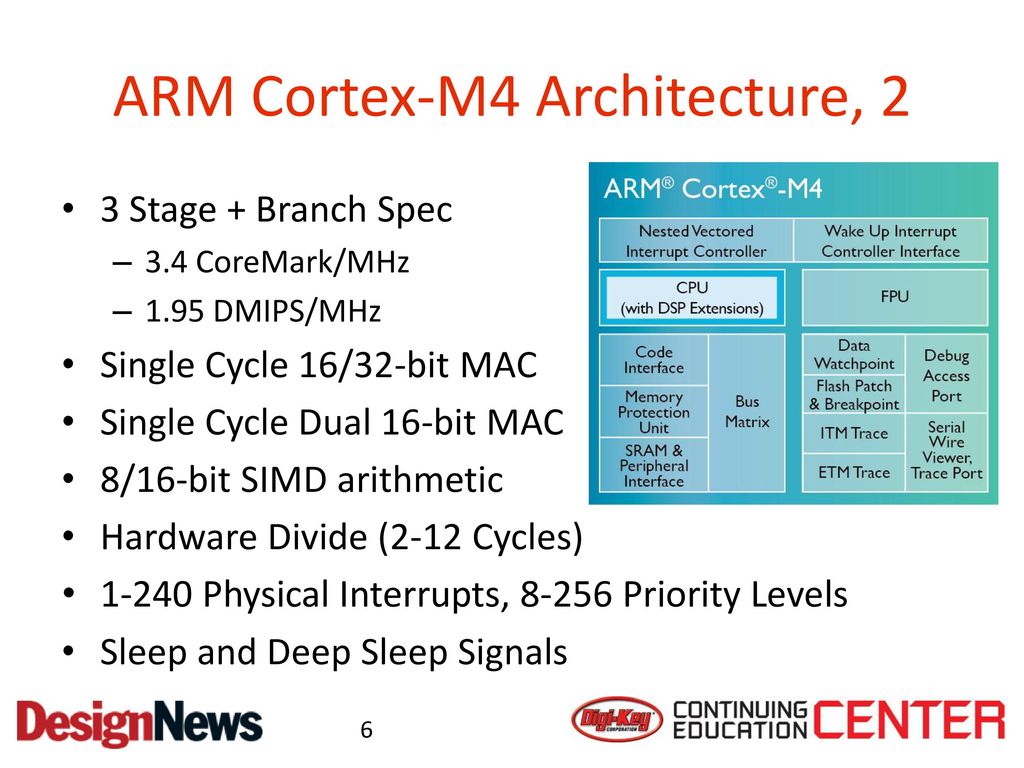

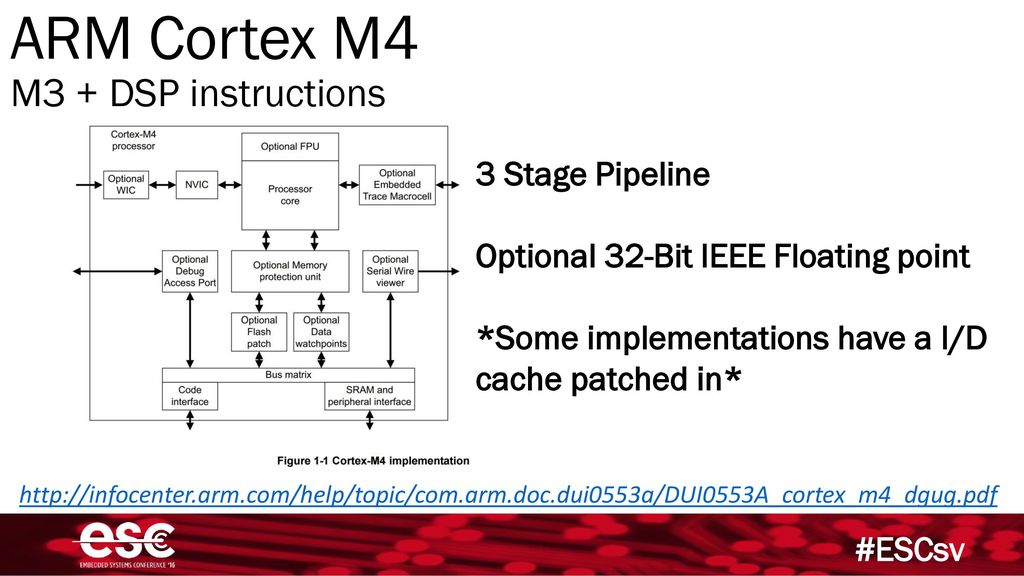

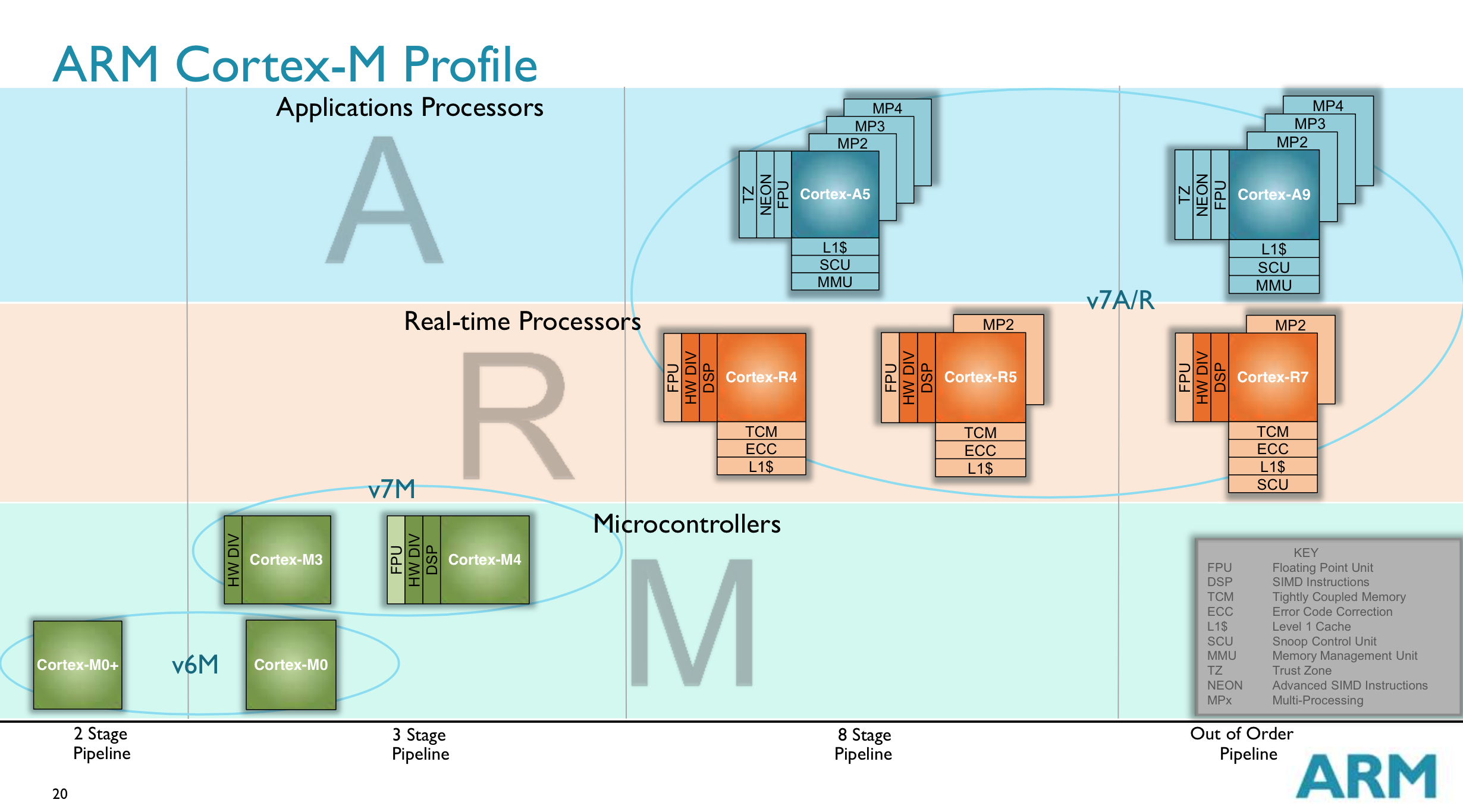

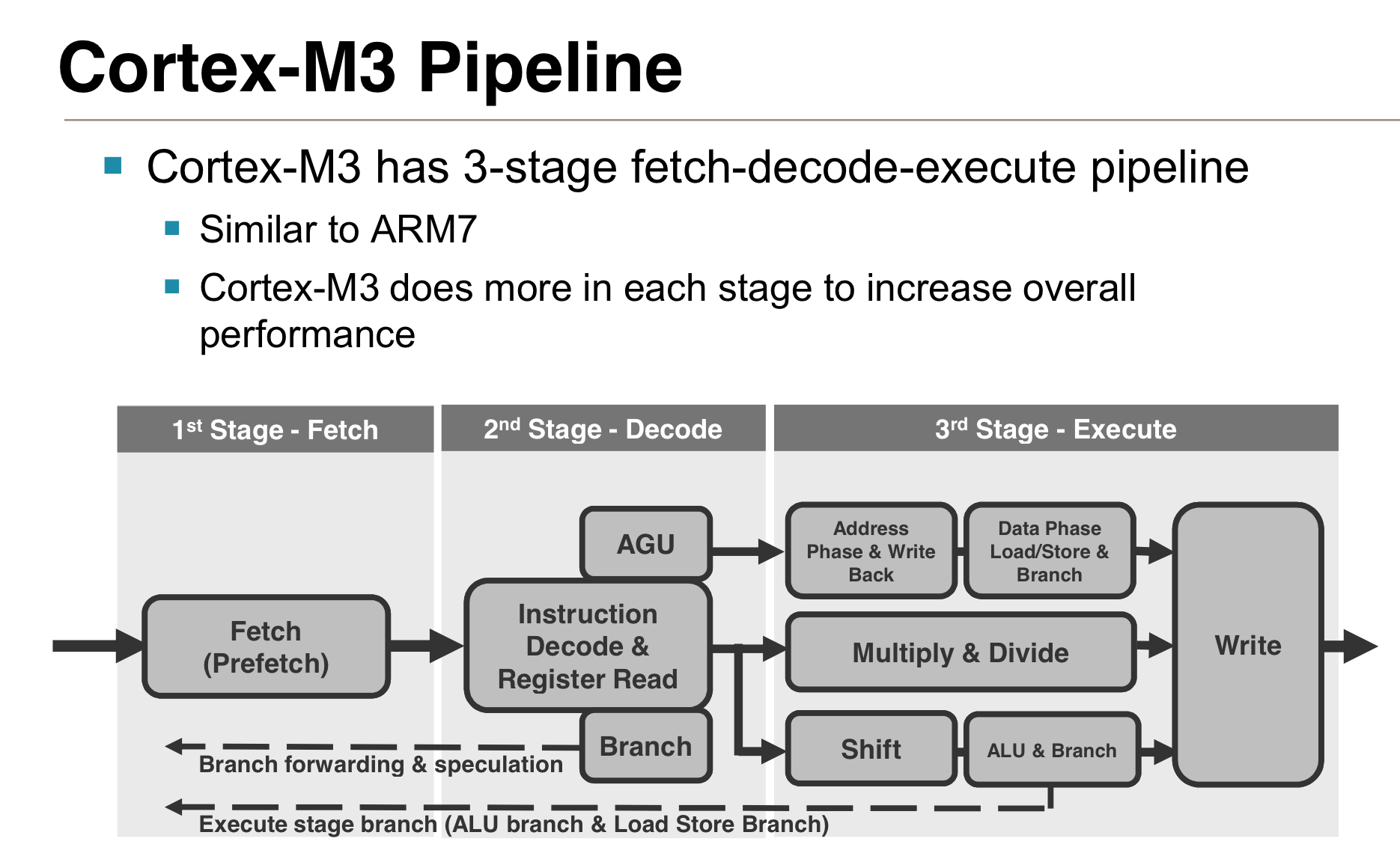

Mprofile, the Microcontroller profile, implemented by most cores in the CortexM series;The 4stage pipeline enables the CortexM55 processor to have a modest increase in maximum clock frequency compared to the popular CortexM4 processor (typically over 10% depending on the configuration) 42 Floatingpoint Unit The CortexM55 FPU support is based on Arm FPv5 architecture which is fully IEEE754 compliant When the FPU isView ARM CortexM4 Processor Architecturepdf from COMPUTER S 2334 at Tshwane University of Technology Embedded Systems Design EBD117V/HWD401T/ADK401T ARM CortexM4 Processor Architecture 30 January

Cortex M4 Part1 Arm Architecture Instruction Set

Arm cortex m4 architecture reference manual

Arm cortex m4 architecture reference manual-Cortex®M4 with FPU processor is the latest generation of Arm®CortexM4 processor Using this book This book is organized into the following chapters Chapter 1 Introduction Read this for a description of the componen ts of the processor, and of the product documentation Chapter 2 Functional Description Read this for a description of the functionality of the processor Chapter 3 Programmers Model Read this for a description of the processor

Chapter 2 Fundamental Concepts

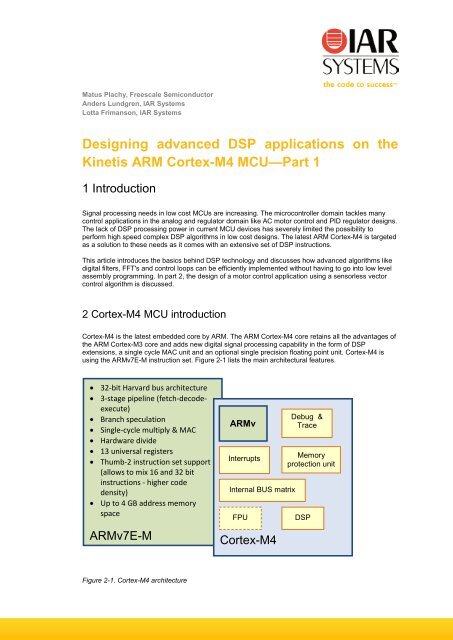

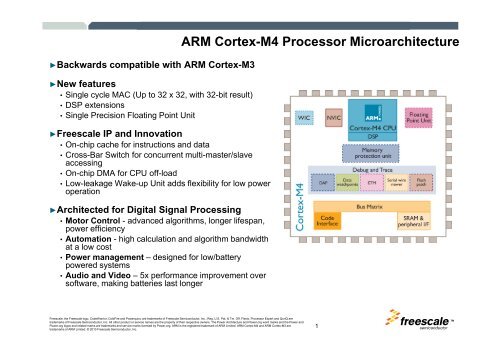

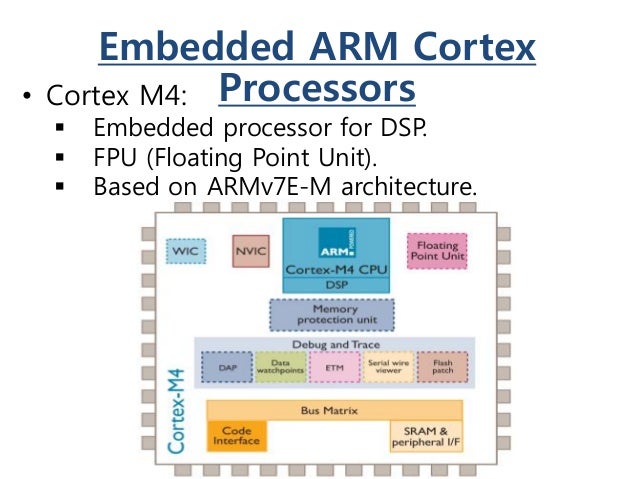

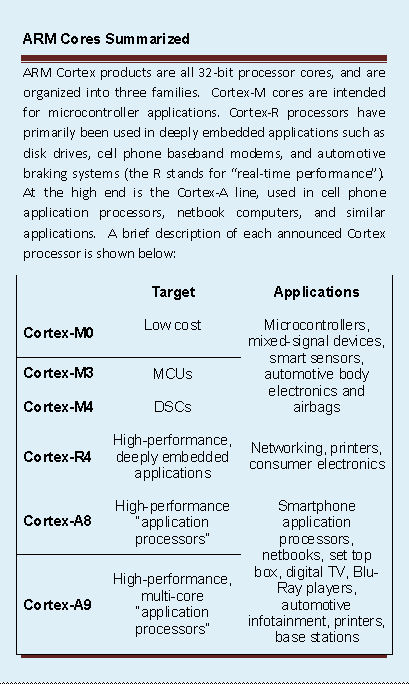

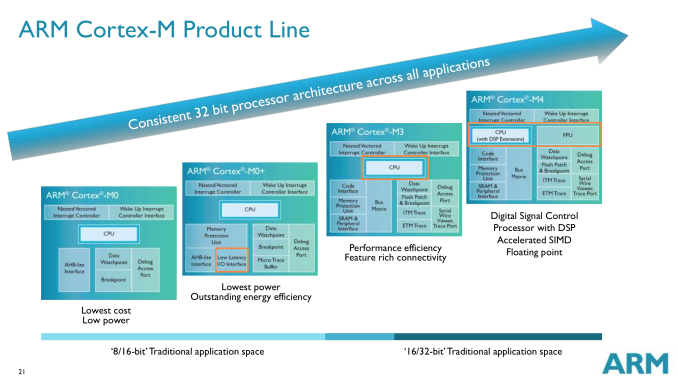

Let MindShare Bring ARM CortexM3/M4 Hardware Design to Life for You This course is designed for those who are designing hardware based around the ARM CortexM0/M0 cores All of MindShare's classroom and virtual classroom courses can be customized to fit the needs of your group ARM CortexM3/M4 Hardware Design Course InfoThis video presents the basics of the CortexM architecture from the programmer's point of view, including the registers and the memory mapThe Arm CortexM4 processor is a highlyefficient embedded processor The CortexM4 processor is developed to address digital signal control markets that demand an efficient, easytouse blend of control and signal processing capabilities

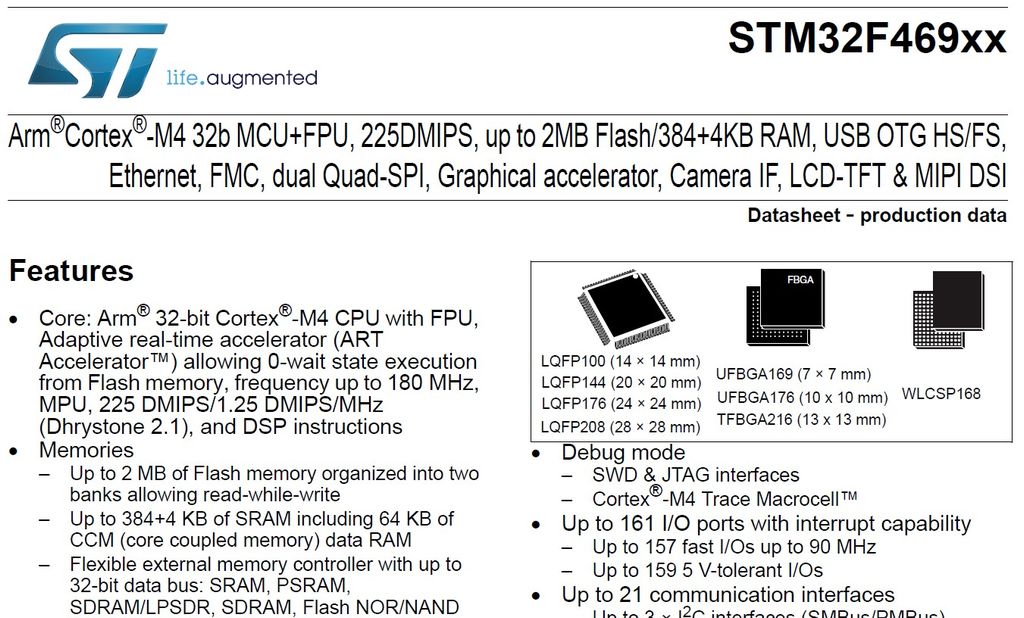

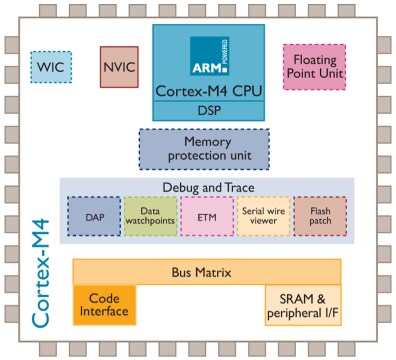

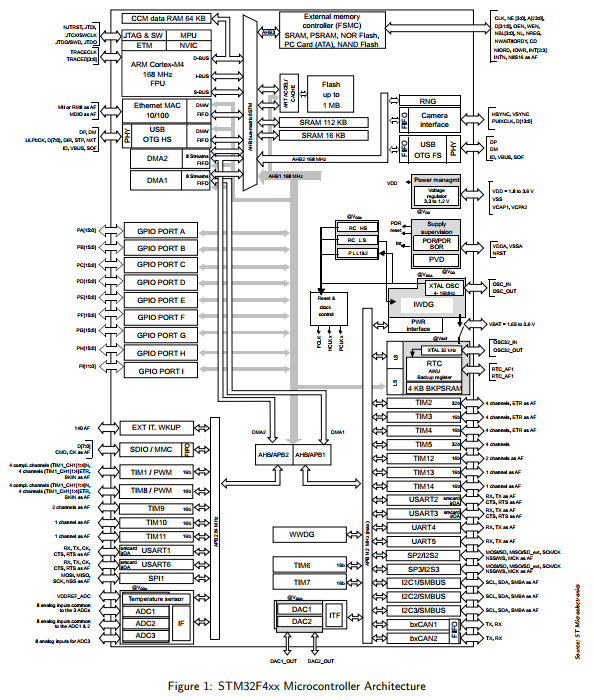

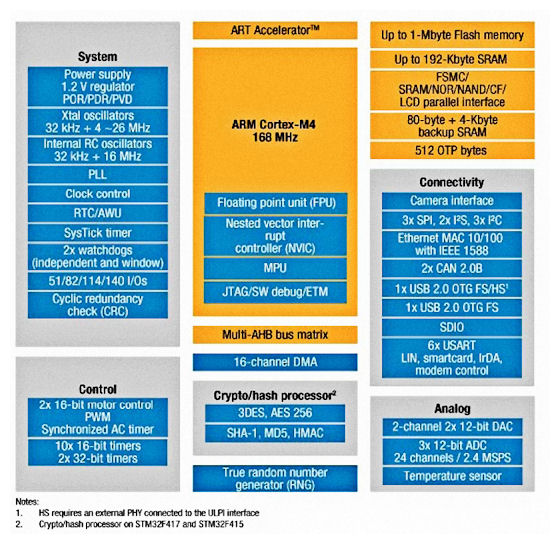

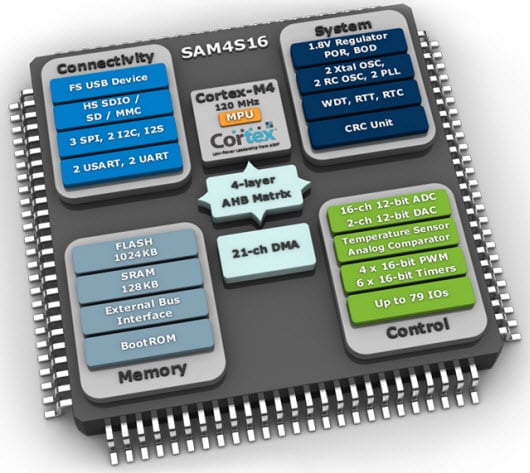

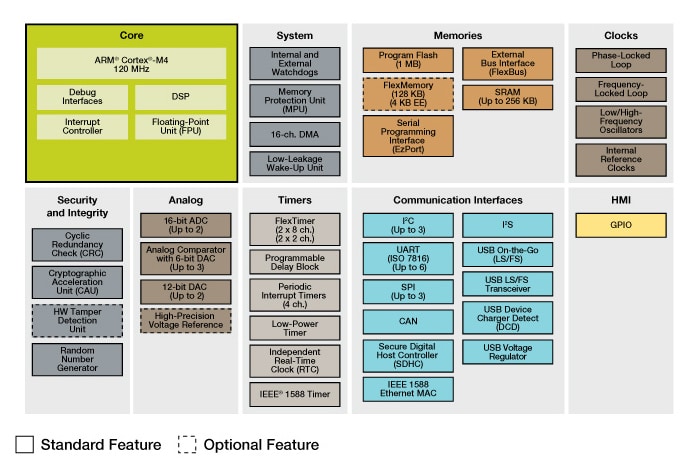

Exceptional performance expected of a modern 32bit architecture, with the high code density of 8bit and 16bit microcontrollers The CortexM4 processor has an optional Memory Protection Unit (MPU) that permits control of individual regions in memory, enabling applications to utilize multiple privilege levels, separating and protecting code, data and stack on a taskbytask basisARM MCU, STM32 Family STM32L4 Series Microcontrollers, ARM CortexM4, 32bit, 1 MHz, 2 MB, 640 KB STMICROELECTRONICS You previously purchased this product View in Order History Each 1 £945 £ 10 £0 £996 25 £795 £9540 50 £748 £76 100 £700 £84 250 £666 £7992 More PricingSearch for jobs related to Arm cortex m4 architecture or hire on the world's largest freelancing marketplace with 19m jobs It's free to sign up and bid on jobs

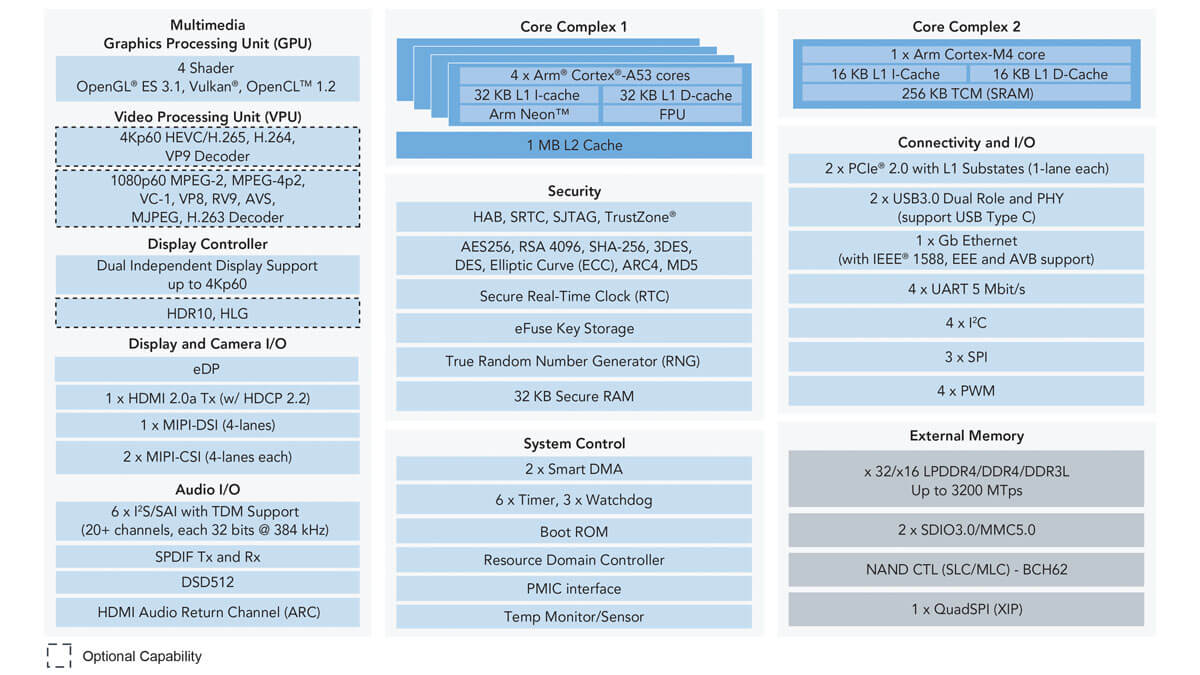

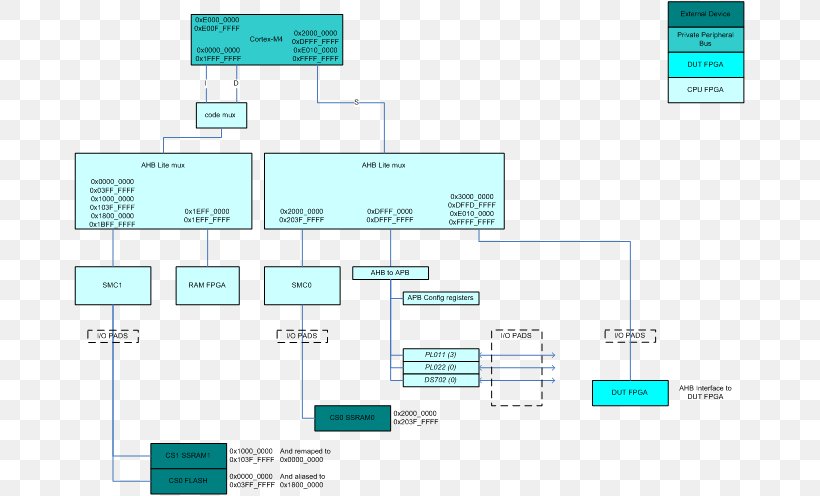

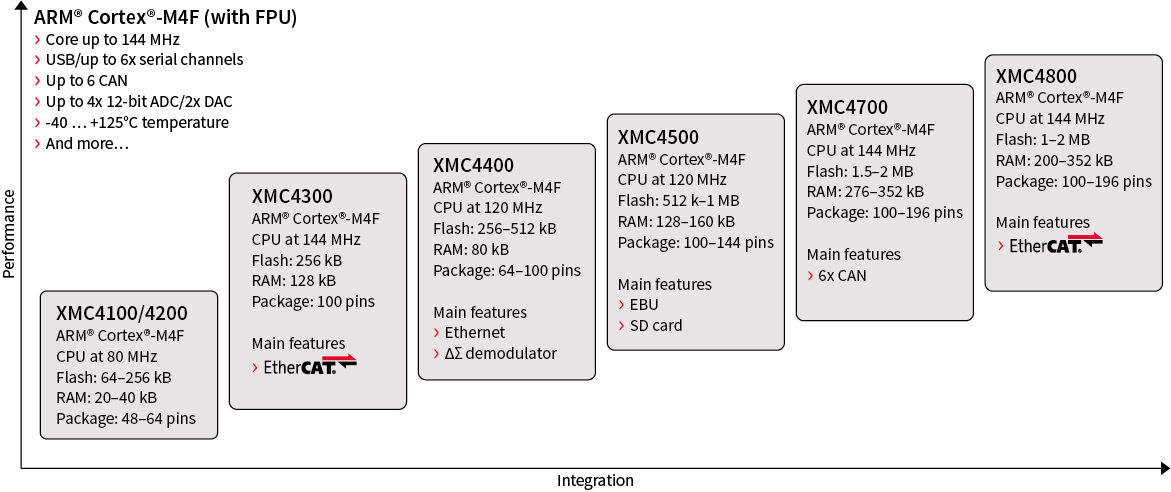

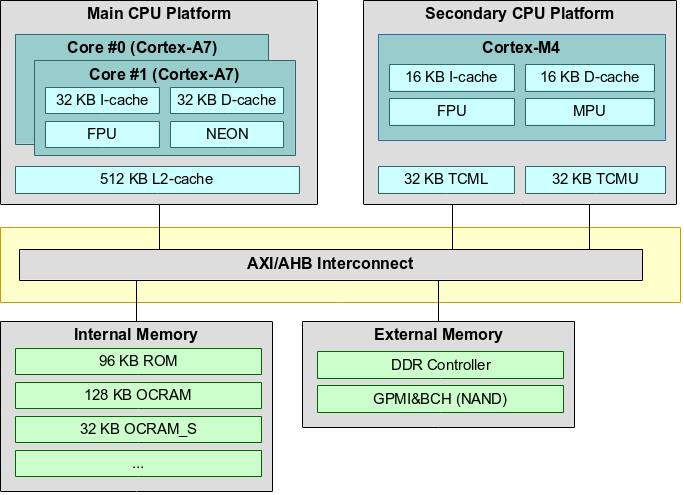

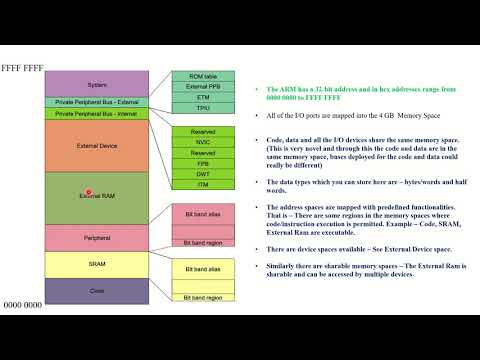

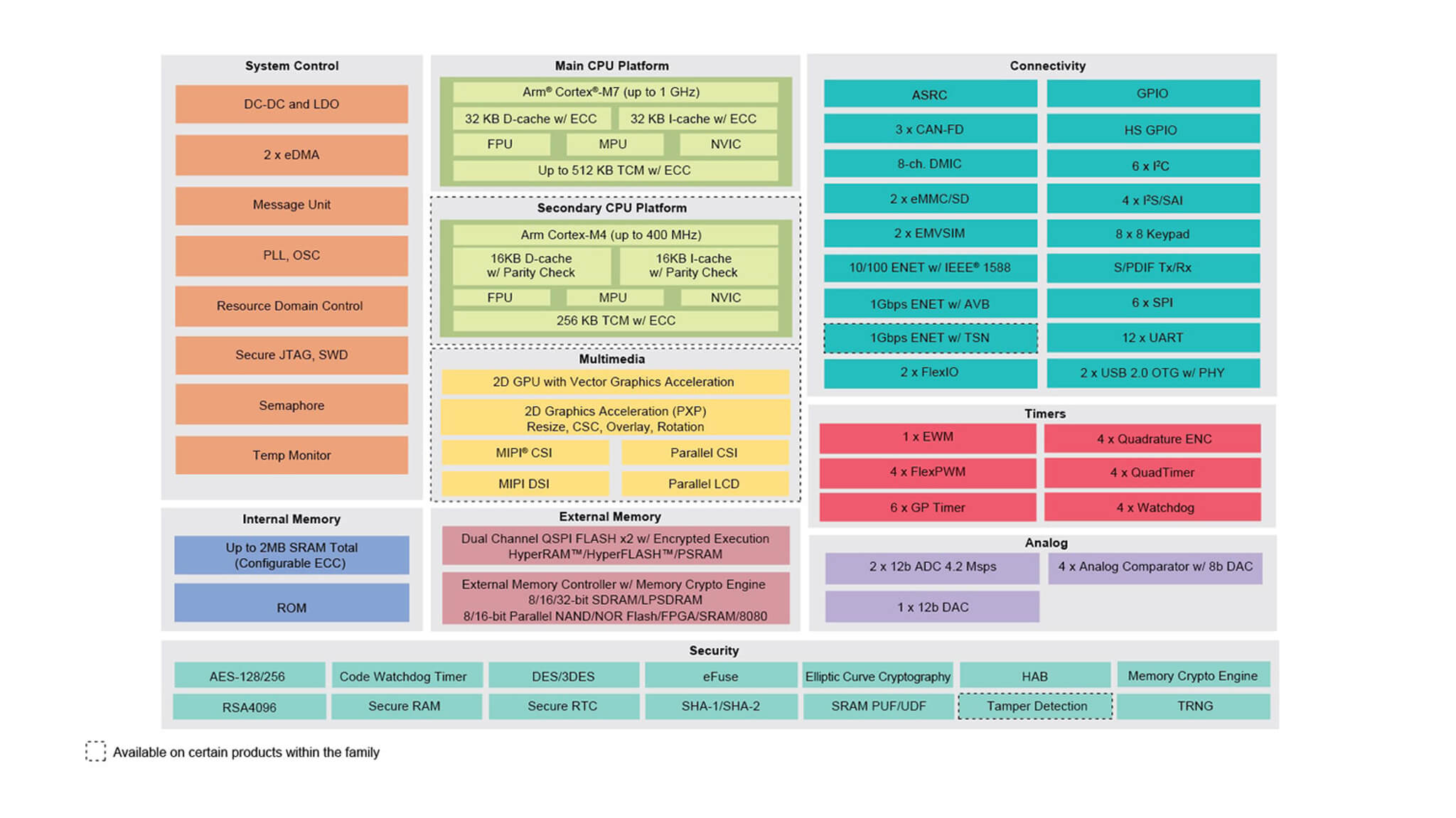

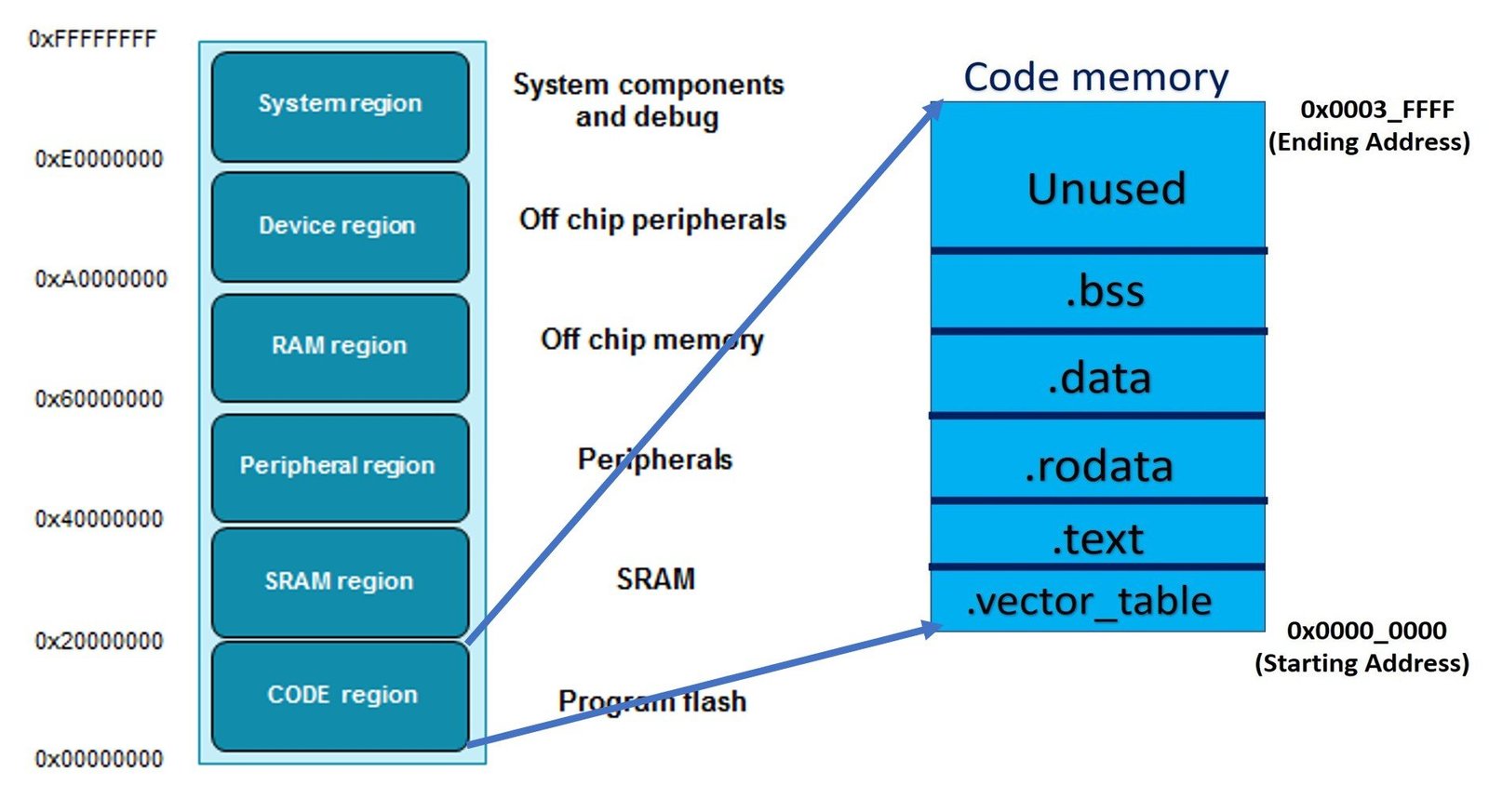

Sep 16, In depth guide on ARM CortexM4 Architecture microcontrollers, comparison of different CortexM family microcontrollers Sep 16, In depth guide on ARM CortexM4 Architecture microcontrollers, comparison of different CortexM family microcontrollers Today Explore When autocomplete results are available use up and down arrows to review andThe CortexM4 core is also able to run from external DDR memory (through the MMDC) and QSPI Furthermore, the CortexM4 uses a Modified Harvard Architecture, which has two independent buses and caches for Code (Code Bus) and Data (System Bus) The memory addressing is still unified, but accesses are split between the buses using addresses asCortexM4 processor, the programmer's model, instruction set, registers, memory map,floating point, multimedia, trace and debug support Product revision status The rmpn identifier indicates the revision status of the product described in this book, for example, r1p2, where rm Identifies the major revision of the product, for example, r1 pn Identifies the minor revision or modification

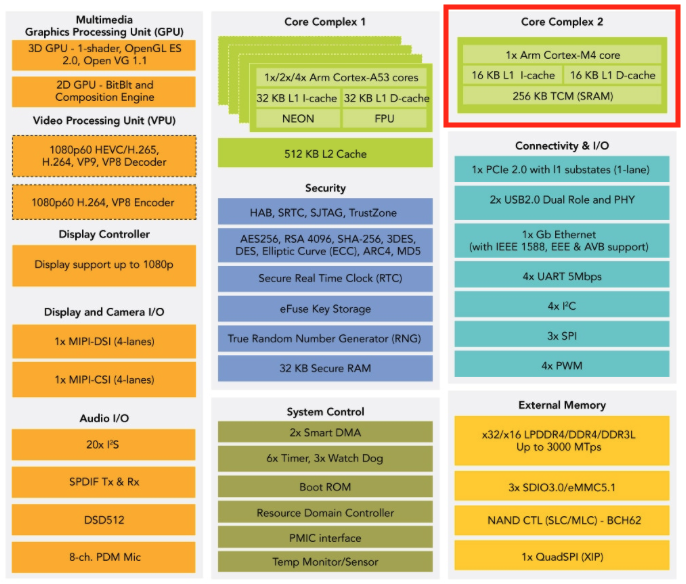

I Mx 8m Applications Processor Arm Cortex A53 Cortex M4 4k Display Resolution Nxp Semiconductors

Designing With Arm Cortex M4 And A Real Dev Board Ppt Download

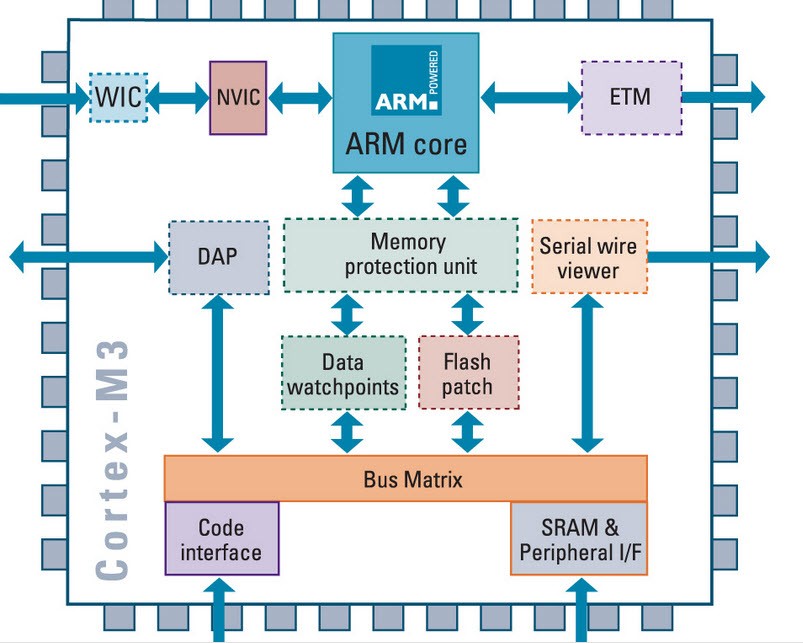

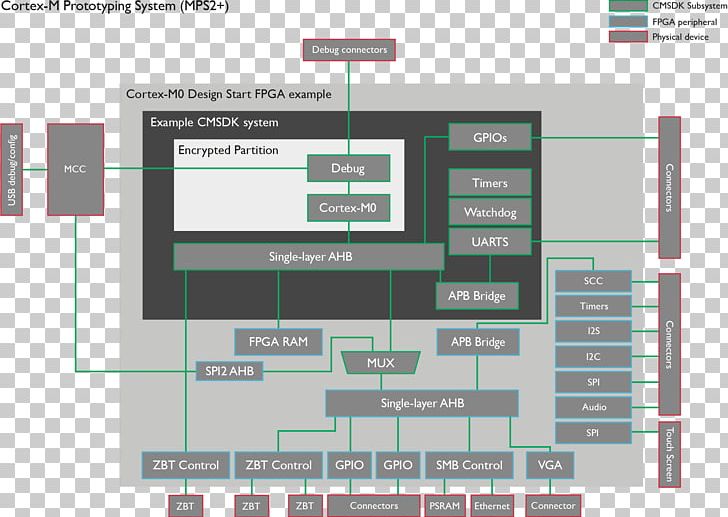

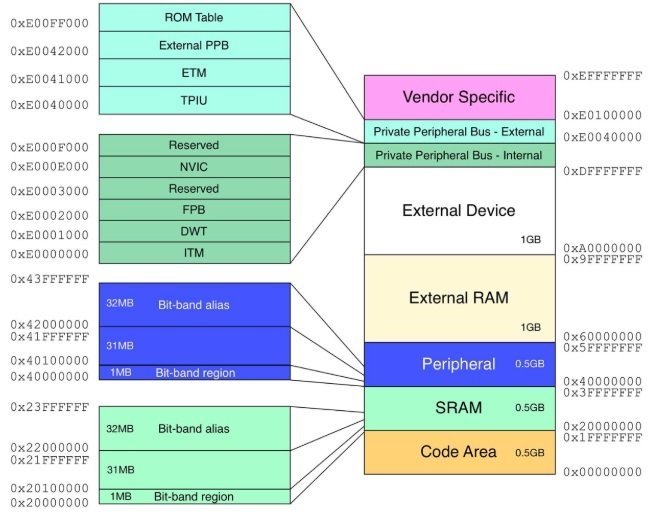

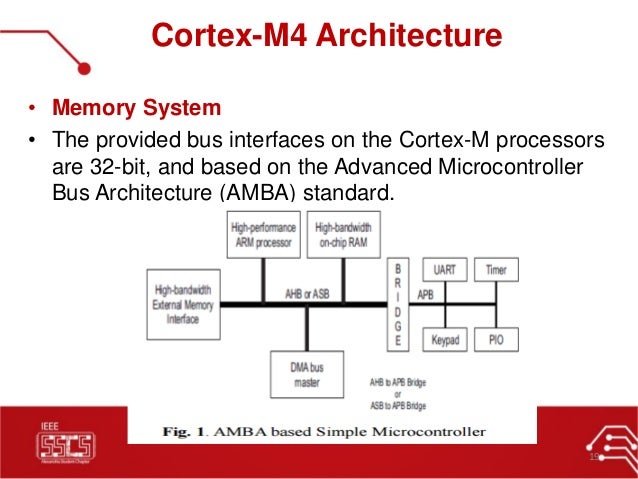

CortexM4 processor is designed to meet the challenges of low dynamic power constraints while retaining light footprints 180 nm ultra low power process –157 µW/MHz 90 nm low power process –33 µW/MHz 40 nm G process –8 µW/MHzARM Cortex M Architecture 3 ARM CortexM4 processor Harvard versus von Neumann architecture Different busses for instructions and data • ICode bus Fetch op codes from ROM • System bus Data from RAM and I/O • Dcode bus Debugging • PPB bus Private peripherals 𝐴=𝜋𝑟2 ARM Cortex M Architecture Texas Instruments Reduced Instruction Set Computer (RISC) 4DOCUMENTATION MENU DEVELOPER DOCUMENTATION Back to search

What Is Arm Processor Arm Architecture And Applications

Arm Cortex M4 Introduction Binh Pham Blog

Here, we can understand the features and architectural details of ARM CORTEX M4CortexM4 hardware implementation Although the CortexM4 seems to be a simple 32bit core, it supports sophisticated mechanisms, such as exception preemption, internal bus matrix and debug units Through a tutorial, the CortexM4 low level programming is explained, particularly theAlthough the architecture profiles were first defined for ARMv7, ARM subsequently defined the ARMv6M architecture (used by the Cortex M0/M0/M1) as a subset of the ARMv7M profile with fewer instructions CPU modes

Arm Cortex M Family Introduction

Arm Cortex M4 Arm Holdings Arm Architecture Arm Cortex M3 Softbank Group Blue Text Rectangle Png Pngwing

Cortex®M4 processor core is the first core of the CortexM line up to feature dedicated Digital Signal Processing (DSP) IP blocks, including an optional FloatingPoint Unit (FPU)CORTEX®M3 and CORTEX®M4 Processors (Third Edition), 14 1467 ROM table CoreSight™ Debug Architecture is very scalable and can be used in complex SystemonChip designs with a large number of debug components In order to support a wide range of system configuration, CoreSight Design Architecture provides a mechanism toARM Processor Architecture Embedded Systems with ARM CortextM Updated Monday, February 5, 18 A Little about ARM –The company •OriginallyAcorn RISC Machine (ARM) •LaterAdvanced RISC Machine •Then it became ARM Ltd owned by ARM Holdings (parent company) •In 16 SoftBankbought ARM for $31 billion •ARM • Develops the architecture and licenses it

Arm Architecture Arm Cortex M4 Microcontroller Field Programmable Gate Array Png 673x496px Arm Architecture Area Arm

Arm Cortex M4 Arm Architecture Computer Architecture Microprocessor Png Clipart Arm Cortexa72 Arm Cortexm Arm Cortexm4

The PSoC 6 family is built on an ultralowpower architecture, and the MCUs feature lowpower design techniques to extend battery life up to a full week for battery powered applications The dualcore Arm®Attendees will get a quick overview of the ARM CortexM4 CPU architecture and how to use its key features to implement common MCUbased designs The instructor, Warren Miller, will present a comparison to other ARM CPU families to help round out the attendee's understanding of this important CPU family Miller has more than 30 years of experience inCortex®M3/M4 SoC Design is a 3day class for engineers designing hardware based around the ARM CortexM3/M4 core It includes an introduction to the ARM product range and supporting IP, programmer's model, instruction set architecture, AMBA onchip bus architecture and CortexM3/M4 debug architecture The class includes a number of

Datasheet Review High Performance Stm32 Cortex M4 Microcontroller

Eli Hughes Dsp Development With The Arm Cortex M4 And M7 Cores Eli Hughes Ppt Download

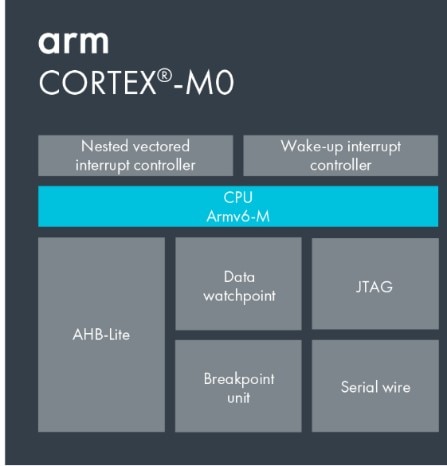

The CortexM processor series is designed to enable developers to create costsensitive and powerconstrained solutions for a broad range of devices CortexM4 is a highperformance embedded processor developed to address digital signal control markets that demand an efficient, easytouse blend of control and signal processing capabilities$ armnoneeabireadelf A exampleo Attribute Section aeabi File Attributes _CPU_name CortexM4 _CPU_arch v7EM _CPU_arch_profile Microcontroller _THUMB_ISA_use Thumb2 _FP_arch VFPv4D16 _ABI_PCS_wchar_t 2 _ABI_FP_denormal Needed _ABI_FP_exceptions Needed _ABI_FP_number_model IEEE 754 _ABI_align_needed 8Processors for embedded systems It was developed to provide a lowcost platform that meets the needs of MCU implementation, with a reduced pin count and lowpower consumption, while delivering outstanding computational performance and an advanced response to interrupts The Arm®

Arm Cortex M0 Silicon Labs

Arm Cortex M0 Microcontrollers Stmicroelectronics

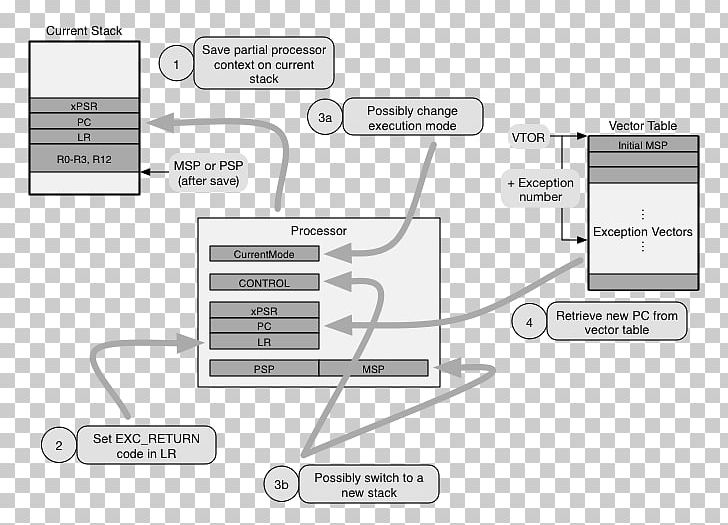

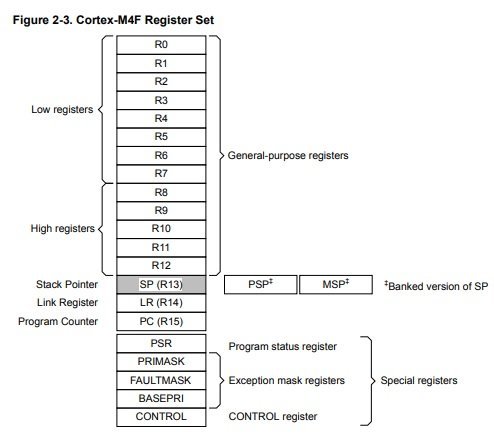

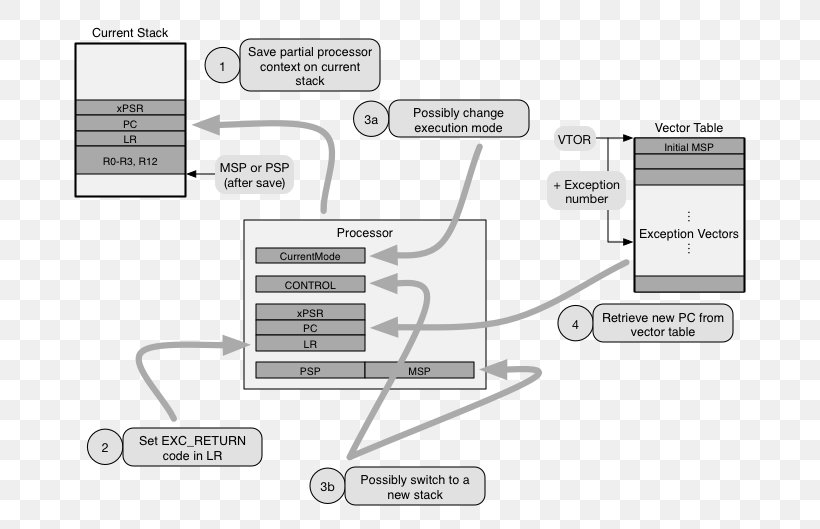

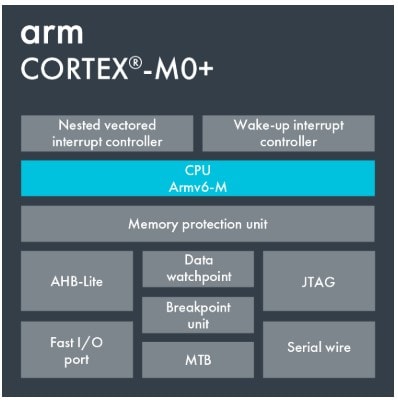

The dualcore architecture of PSoC 6 is ideal for establishing isolated processing environments The CortexM4 processor is used to establish a NonSecure Processing Environment (NSPE) and the CortexM0 is used to establish a Secure Processing Environment (SPE) through the use of protection units built into PSoC 6 Trusted FirmwareM running in the SPE communicates to theArchitecture Diagram 17 Registers ARM has a load store (RISC) architecture General purpose registers can hold data or address In Arm cortexM4 there are 21 Registers Visible each 32bit wide Sixteen registers located in the register bank Five special registers located outside of the register bank 18Cortex®M4 and CortexM0 architecture lets designers optimize for power and performance simultaneously

Cortex M4 Technical Reference Manual

Var Som Mx7 Freertos For M4 Variscite Wiki

ARM designed the CortexM4 architecture in a way it is possible to have a FPU added For example the NXP ARM CortexM4 on the FRDMK64F board has a FPU present MK64FN1M0VLL12 on FRDMK64F The question is how long willJoseph Yiu, in The Definitive Guide to ARM®M4 MCU Architecture Introduction Many embedded developers are familiar with the ARM Cortex processor architecture, but few have the opportunity to become intimately acquainted enough of this popular architecture to take full advantage of its unique features and capabilities This is especially true for the new ARM CortexM4 processor, which boasts an improved architecture

Arm S Cortex M Even Smaller And Lower Power Cpu Cores

Chapter 2 Fundamental Concepts

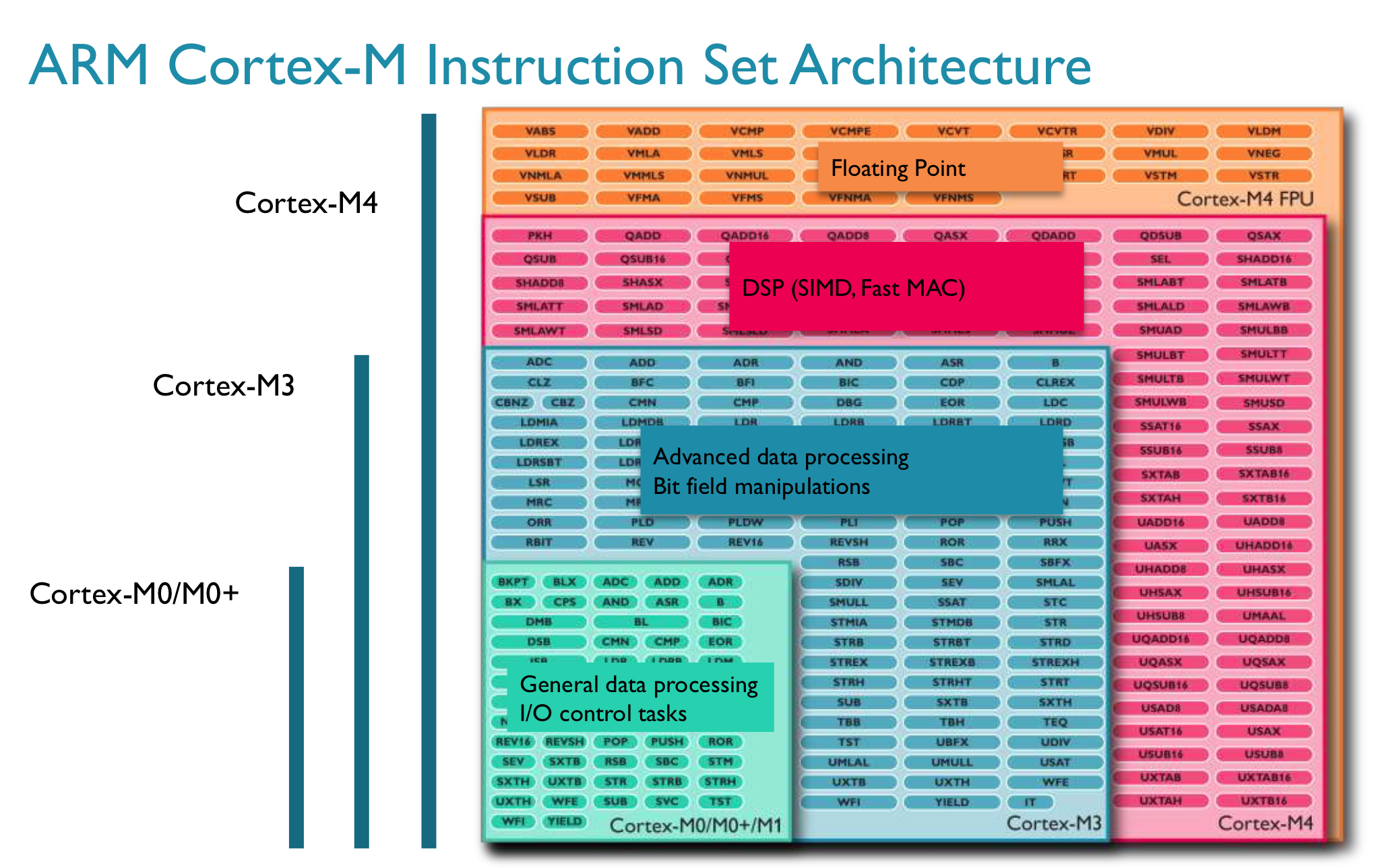

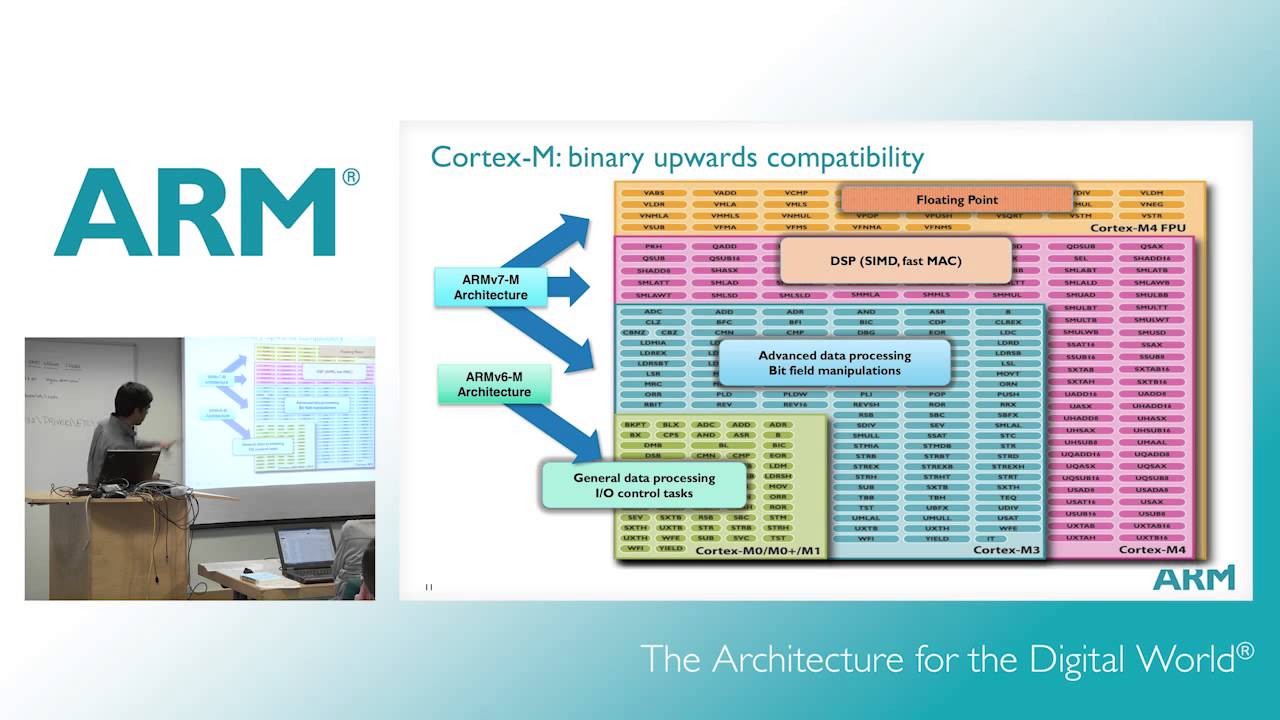

Cortex M4 also provides instruction sets of ARM 32 bit type, Thumb 16 bit and Thumb 2 But it also includes range of saturating and SIMD instructions specifically optimized to handle DSP algorithms Cortex M3 does not have a floating point unit Cortex M4 provides an optional floating point unit and in such cases the cores are denoted as M4FArchitecture ARM v6M eg CortexM0, M1 eg ARM7TDMI eg ARM9926EJS eg ARM1136 ARMv8 ARMv7A Architecture eg Cortex ARMv7R eg CortexR4 ARMv7M eg CortexM3 ARMv8A eg CortexA53 CortexA57 ARMv8R As of Sept 13CortexM4 software implementation and debug ;

Fast Track Exercises To Understand Arm Cortex M4 Architecture Using Texas Instruments Stellaris Launch Pad Science Publishing Group

Arm Cortex M Wikipedia

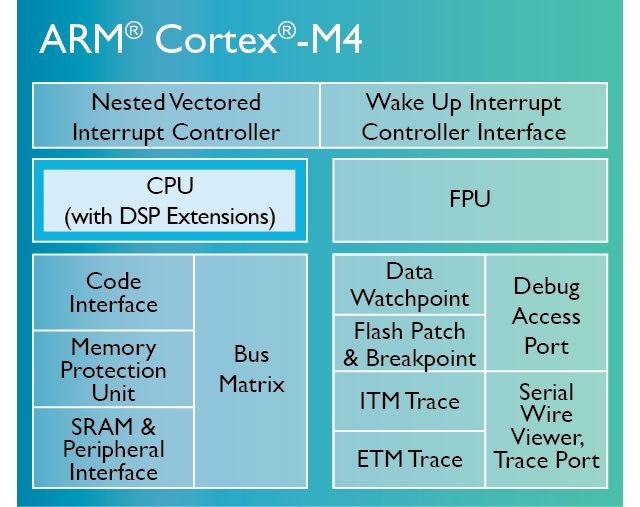

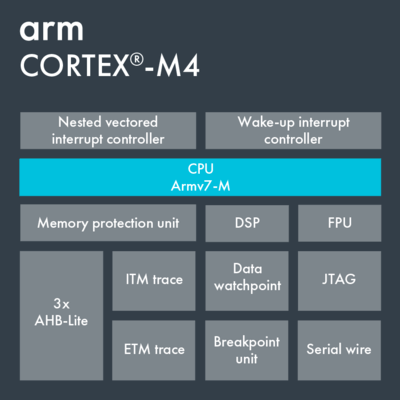

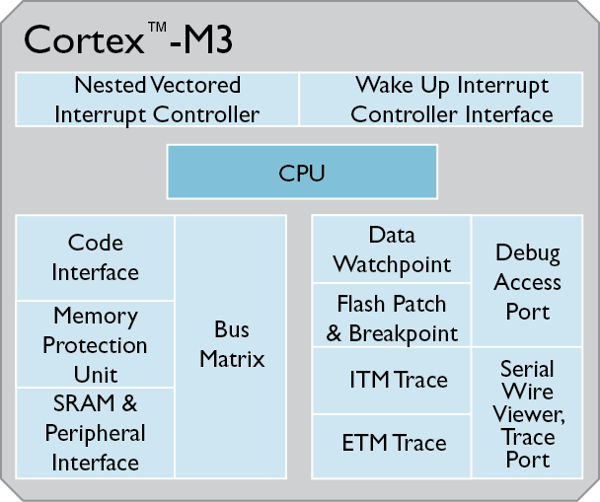

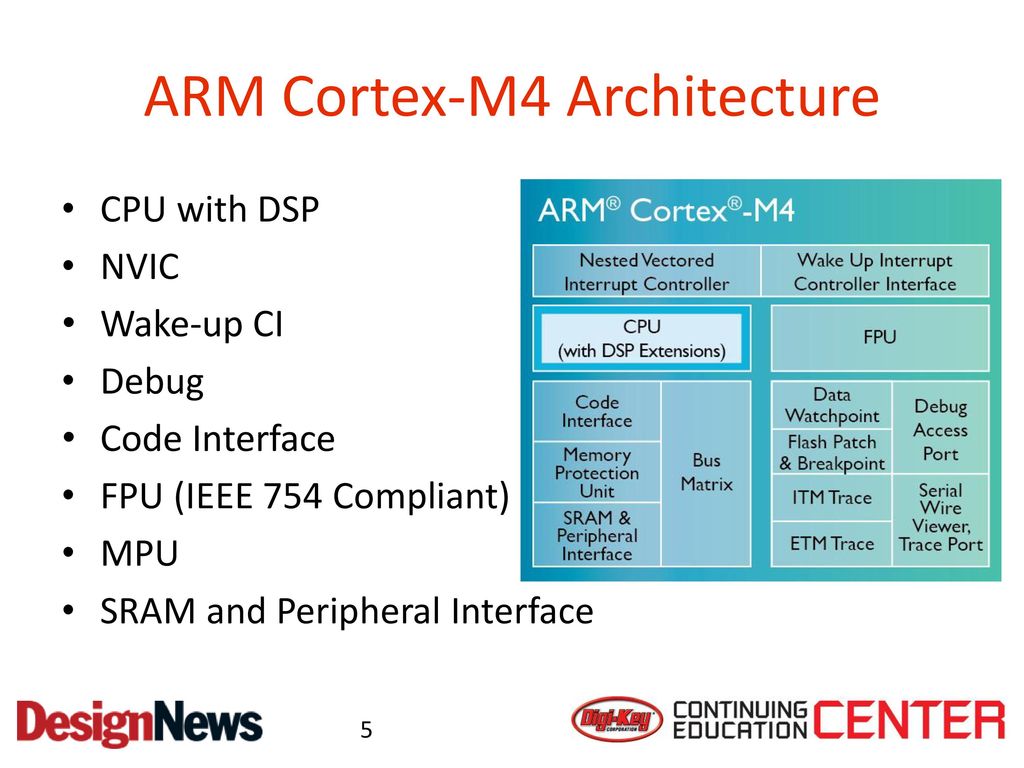

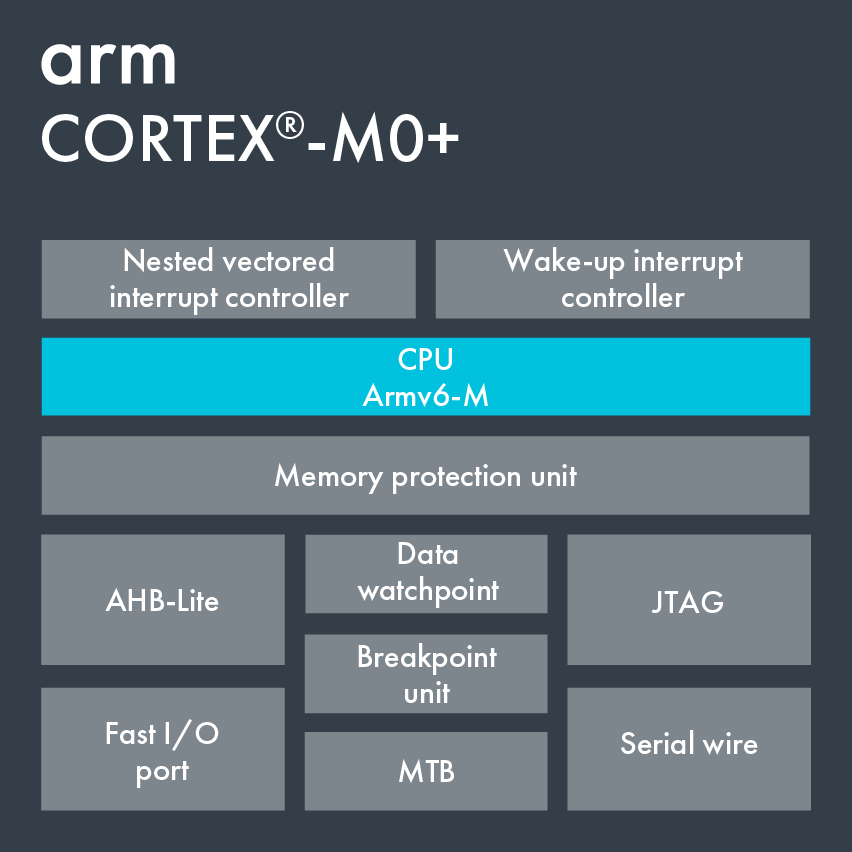

M0 instruction set architecture vs M4 instruction set architecture M0 uses the Armv6M architecture which has a smaller instruction set and offers less hardware support This means mathematical calculations are more labour intensive on this chip The richer CortexM4 instruction set means there's hardware support for a number of the key operations needed toThe CortexM4 CPU has two buses connected to the main interconnect (modified Harvard architecture) One bus is meant to fetch data (system bus) whereas the other bus is meant to fetch instructions (code bus) To get optimal performance, the program code should be located and linked for a region which is going to be fetched through the code bus, while the data areaCortexM4 Architecture Block Diagram The M4 CPU is at the heart of it's operation and NVIC, Bus Interconnect, Debug system and Memory Protection Unit are other important functional blocks CortexM4 Architecture Block Diagram Processor Core • Contains internal registers, the ALU, data path and some control logic • Registers include sixteen 32bit registers for both general and

Cortex M4 Part1 Arm Architecture Instruction Set

Arm Cortex M4 Arm Architecture Exception Handling Arm Cortex M3 Png Clipart Angle Area Arm Architecture

CortexM4 It provides all the features on the CortexM3, with additional instructions target at Digital Signal The Instruction Set Architecture (ISA) is a part of the processor architecture, and the CortexM processors can be grouped in several architecture profiles Architecture Descriptions ARMv6M For CortexM0, CortexM0 and CortexM1 processors ARMv7M For CortexM3, CortexM4CortexM4 Instruction Set • CortexM4 processor – ARMv7M architecture – Supports 32bit Thumb2 instructions – Possible to handle all processing requirements in one operation state (Thumb state) – Compared with traditional ARM processors (use stateswitching), advantages include * No state switching overhead – both execution time and instruction spaceNote that implementations of the same architecture can be different CortexA8 architecture v7A, with a 13stage pipeline Cortex architecture v7A, with an 8stage pipeline Thumb2 Architecture Profiles 7AApplications 7R Realtime 7M Microcontroller v4 v5 v6 v7 Development of the ARM Architecture

Architecture Features Of Arm Cortex M4 Cute766

Cortex M4 Arm Developer

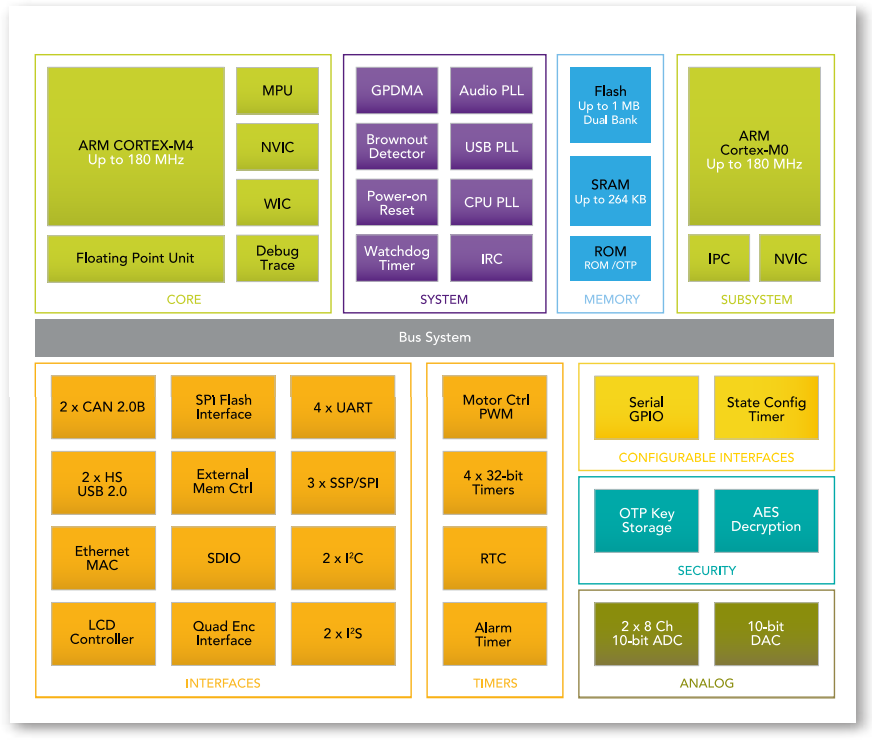

The CortexM0 coprocessor offloads many of the data movement and I/O handling duties that can drain the bandwidth of the CortexM4 core With its dualcore architecture and unique set of configurable peripherals, NXP Semiconductors LPC4300 MCUs enable development of a wide range of applications, such as motor control, power management, industrial automation, robotics,CortexM3 processor architecture and features The CortexM3 processor, based on the ARMv7M architecture, has a hierarchical structure It integrates the central processor core, called the CM3Core, with advanced system peripherals to enable integrated capabilities like interrupt control, memory protection and system debug and trace These peripherals are highly configurable to allow the CortexThe CortexM series is built on the ARMv7M architecture (used for CortexM3 and CortexM4), and the smaller CortexM0 is built on the ARMv6M architecture The first CortexM processor was released in 04, and it quickly gained popularity when a few mainstream MCU vendors picked up the core and started producing MCU devices It is safe to say that the CortexM has become

Introduction

Arm Cortex M4 Microcontrollers Mouser

Product Range Architecture MCU Core Size Program Memory Size RAM Memory Size CPU Speed No of I/O's MCU Case Style No of Pins Embedded Interface Type MCU Applications Supply Volt

The Architecture Of The Stm32f4xx Microcontroller Chegg Com

Freertos On The Cortex M4 Of A Verdin Imx8m Mini

Arm Cortex M3 And Cortex M4 Definitive Guide Chapter Iv Notes Programmer Sought

Lpc4300 Cortex M4 M 0 Dual Core Mcus Nxp Semiconductors Mouser

Arm Cortex M4 Cookbook Fisher Dr Mark Amazon Com Books

Cypress Psoc 6 Dual Core Arm Cortex M4 And Arm Cortex M0 Youtube

Arm Cortex M Wikipedia

Figure 1 From Embedded Systems And Internet Of Things Iots Challenges In Teaching The Arm Controller In The Classroom Semantic Scholar

More On Fast Interrupt Handling With Cortex M4 Big Mess O Wires

Cortex Core An Overview Sciencedirect Topics

Arm Cortex M4 Architecture Microcontrollers Programming

Ingenious Architectural Features Allow St To Extract Maximum Performance From New Microcontroller Family Based On Arm Cortex M4 Cost Less Than 6 Bucks In 1000s Eda360 Insider

Arm Cortex M4 Architecture Microcontrollers Programming

3 Advantages To Using A Multicore Microcontroller Designnews Com

Memory Considerations For Faster Mcus Digikey

32 Bit Xmc4000 Industrial Microcontroller Arm Cortex M4 Infineon Technologies

I Mx 7 Cortex M4 Memory Locations And Performance Yet Another Tech Blog

Arm Cortex M4 Core Registers

Stm32f479ng High Performance Advanced Line Arm Cortex M4 Core With Dsp And Fpu 1 Mbyte Of Flash Memory 180 Mhz Cpu Art Accelerator Chrom Art Accelerator Fmc With Sdram Dual Qspi Tft Mipi Dsi Hw

Arm Cortex M4 Architecture Microcontrollers Programming

Designing Advanced Dsp Applications On The Kinetis Arm Cortex

Isystem Webinar Debug And Trace On Cortex M4 Based Microcontrollers With Isystem Tools Youtube

Are The Arm Cortex Mx Processors Harvard Or Von Neumann Architecture Quora

Main Stack Pointer An Overview Sciencedirect Topics

Arm Cortex M4 Processor Microarchitecture

The Definitive Guide To Arm Cortex M3 And Cortex M4 Processors Yiu Joseph Ebook Amazon Com

Arm Cortex M4 Microcontrollers Mouser

Taking The Risc Out Of Cisc Digikey

Arm Cortex M

Cortex M4 Technical Reference Manual

Selecting The Right Microcontrollers For Your Products 8 Bit V S 32 Bit Mcu

Arm S Cortex M Even Smaller And Lower Power Cpu Cores

The Relationship Between Cortex M4 Core And Stm32 Programmer Sought

Stm32f423zh High Performance Access Line Arm Cortex M4 Core With Dsp And Fpu 1 5 Mbyte Of Flash Memory 100 Mhz Cpu Art Accelerator Dfsdm Aes Stmicroelectronics

Introduction To Arm Architecture

3 Arm Cortex M4 M3 Memory Mapping Youtube

Cortexfamily

What Is The Top Level Difference In Features Between Cortex M33 And Cortex M4 Trustzone For Armv8 M Forum Trustzone For Armv8 M Arm Community

Nxp Develops Dual Core Ghz Crossover Mcu For Edge Ml Embedded Computing Design

Arm Cortex M4 Based Mcus Integrate Lcd Controller Offer Spi Flash Interface Edn

Cortex M Processors And The Internet Of Things Iot

Video Tutorial On Arm Cortex M Series Debug And Trace Youtube

Nxp Mixes Cortex M4 M0 In Dual Core Attack Embedded Com

Adsp Cm408f Datasheet The Adsp Cm408f Mixed Signal Control Processor Integrates

Max Ultra Low Power Arm Cortex M4 With Fpu Based Microcontroller Mcu With 3mb Flash And 1mb Sram Maxim Integrated

Block Diagram Of Cortex M3 Processor Architecture Download Scientific Diagram

Arm S Cortex M Even Smaller And Lower Power Cpu Cores

Psoc 64 Microcontrollers Arm Cortex M4 M0

Arm Cortex M4 Microcontrollers Stmicroelectronics

Chapter 2 Fundamental Concepts

Arm Cortex M4 Arm Architecture Exception Handling Arm Cortex M3 Png 716x529px Arm Cortexm Arduino Area

Arm Cortex M4 Core And Tiva C Series Peripherals Springerlink

Arm Introduces Cortex M4 Core For Digital Signal Controllers Berkeley Design Technology Inc

Arm Cortex M4 Kinetis K64 1 Mhz 32 Bit Mcus Nxp Semiconductors

How To Transition From Basic Microcontrollers To Arm Cortex Electrical Engineering Stack Exchange

Learn The Fundamentals Of Arm Cortex M0 Processor And Designstarttm Hd Youtube

Psoc 63 Microcontrollers Arm Cortex M4 M0

Armv6 M Vs Armv7 M Unpacking The Microcontrollers Processors Blog Processors Arm Community

02 Arm Cortex M4 Specs Ieee Sscs Alexsc

Designing With Arm Cortex M4 And A Real Dev Board Ppt Download

I Mx Rt1170 Crossover Mcu Family With Arm Cortex M7 And Cortex M4 Cores Nxp Semiconductors

Arm Cortex M4 Core And Tiva C Series Peripherals Springerlink

Arm Cortex M Family Introduction

Arm Architecture Wikipedia

Sequence Of Interrupt Processing Steps Arm Cortex M Microcontrollers

M7 Processor An Overview Sciencedirect Topics

Arm S Cortex M Even Smaller And Lower Power Cpu Cores

Cortexfamily

Psoc 62 Microcontrollers Arm Cortex M4 M0

Arm Cortex M0 Microcontrollers Stmicroelectronics

0 件のコメント:

コメントを投稿